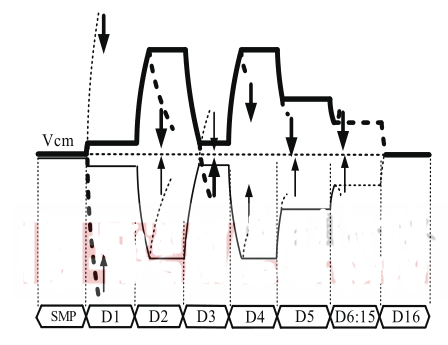

由于P端电压大于N端,因此第二次比较器比较结束后,P端主DAC电容阵列的最高位电容C 1 下极板会从V cm 接到低电位地,N端电容C 1 下极板会从V cm 接到高电位V REF ,同时PN两端的辅助电容阵列次高位电容CC2 继续朝相反方向随机切换。

假设第二次电容切换后P端电压仍大于N端电压,在第三次比较结束后,P端主DAC电容阵列的次高位电容C 2 下极板会从 V cm 接到低电位地。N端电容C2 下极板会从 V cm 接到高电位V REF ,同时PN两端的辅助电容阵列次电容C C3 继续朝相反方向随机切换。即主DAC电容阵列的切换一定是朝着V cm 的方向进行,而辅助DAC电容阵列的切换一直都是随机并且PN两端朝着相反的方向切换。

以此类推,直到8次比较以后,辅助DAC电容阵列下极板均连接 V cm ,主DAC电容阵列剩下还未切换的电容按着 V cm -based切换方式进行切换,最终得到两个ADC分别量化产生的不同的16位码字 D iA 和 D iB 。将两个输出码字 D iA 与 D iB 的差值作为误差信号连接到LMS ω iB 模块与LMS模块并按照公式2-9与公式2-10进行一次迭代处理。初始权重为设计电容值对应的二进制序列,迭代系数值取2 -16 。通过每次量化结束后的不断迭代,直到最终输出码字D out 的线性度达到要求,即可认为接近实际电容值,消除了电容间的失配。

2、 仿真结果

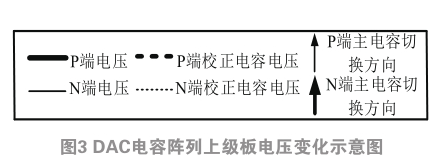

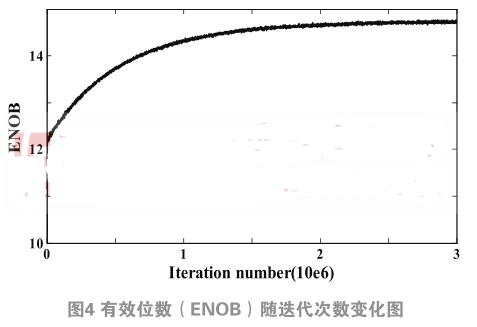

基于第2节的原理介绍,在MATLAB仿真环境中进行了行为级验证,证明了本方法可以有效地消除ADC中电容之间的失配,图3.1与图3.2为一个16位的SAR ADC经过数字后台校正后的结果,单位电容给3%的失配大小,在无校正的情况下有效位数(ENOB)为12.1位,在校正之后提升至14.8位。在无校正的情况下无杂散动态范围(SFDR)为81dB,在校正之后提升至100dB。

3、 结论

随着制造工艺的特征尺寸进入纳米量级,数字电路的集成度越来越高,同时电源电压也逐渐降低。但模拟电路并未像数字电路一样受益于工艺的进步,相反随着MOS管尺寸和电源电压减小,精确匹配、高增益和大摆幅等指标更难实现,因此,采用数字信号处理的方式来解决模拟电路中的非理想因素是一种趋势。本文提出了一种电容失配的数字后台校正方法,能实时跟随环境参数的变化,适用于SAR ADC,能有效消除电容之间的失配,明显地提高ADC性能。