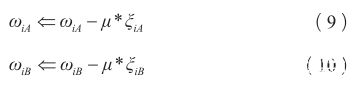

如果差值为零,则权重 ω iA 和 ω iB 就是真实的权重,所得到的量化后的模拟值也是正确的,权重的迭代可以表示为:

其中 μ 为LMS的迭代系数,控制着迭代的速度与精度,一般取2的指数次方。较大的值能使权重更快逼近实际权重,但是容易受到系统噪声的干扰,可能出现迭代错误。较小的值可以得到更精确的权重值,但是需要更多迭代次数,因此需要在速度与精度之间折中考虑。

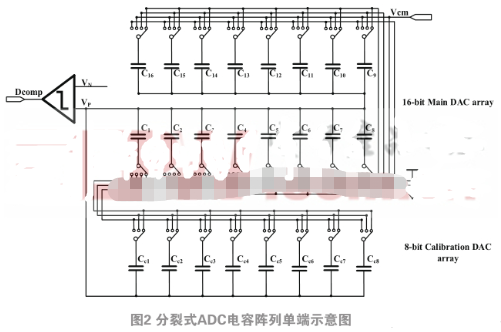

综上所述,本文提出的电容阵列如图2.2所示。为了简化这里只画出单端示意图,另一端与此相同。

图中电容阵列包括16位主DAC电容阵列与8位辅助校正DAC电容阵列,采样方式为电容下级板采样,电容上级板均接在比较器的P输入端。主DAC电容阵列按高位到低位的顺序C 1 ~C 16 的电容值分别为5223C、5223C、5223C、2735C、1432C、750C、393C、206C、108C、57C、30C、16C、8C、4C、2C、1C,其中C为单位电容。辅助DAC同样按照高位到低位的顺序C C1 ~C C8 的电容值分别为8192C、4096C、360C、188C、98C、51C、27C、14C。

基于分裂式ADC的校正算法中两个ADC的工作模式不能完全相同,否则当电容失配方向一致时,码字误差始终为零,无法被校正。为了改变ADC的工作模式,这里通过辅助校正DAC向主DAC注入了一个随机偏移量,从而改变ADC的量化轨迹,提升ADC的线性度和动态范围。同时电容阵列为非二进制编码,引入了冗余量,可以弱化系统在量化过程中引入的动态误差,保证了DAC失配误差校正的可行性。

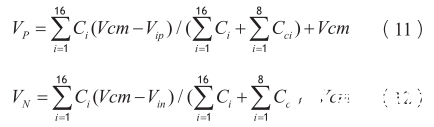

输入信号同时经过两个子ADC模块采样,采样结束后DAC电容上级板电压可表示为:

由于SAR ADC的第一次比较结果只与采样值有关,电容还没有开始切换,这样会导致两个ADC最高位的电容会朝着一个方向切换,因此就无法被校正。这里需要对最高位电容的切换进行单独处理,具体流程如下所述。

采样结束后首先随机切换辅助校正DAC电容阵列最高位电容C C1 ,由于ADC为双端电容阵列,比较器的两个输入端分别连接了DAC电容阵列,因此P端往上切,N端往下切,即P端连接的DAC电容阵列的最高位电容下极板从共模电压切换到更高的电源电压,N端连接的DAC电容阵列的最高位电容下极板从共模电压切换到更低的地电压。因此切换后N端上级板电压小于P端上级板电压,DAC电容阵列的上级板电压变化如图2.3所示。