接收到Global_SYNC脉冲后,可以采用类似以下的流程,计算Σ-ΔADC转换开始和Global_SYNC脉冲之间的不确定性:

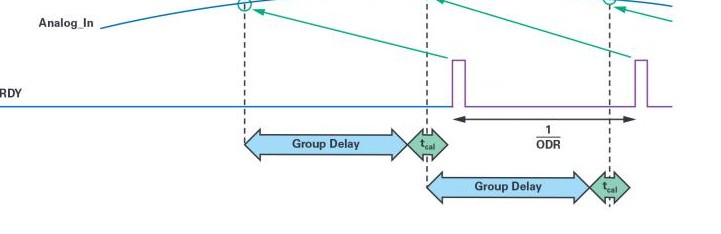

·控制器计算采样时刻(通过了解群延迟从数据就绪信号向后计算,如图8所示)和Global_SYNC脉冲之间的时间差。群延迟是一份数据手册规范,说明从对输入采样到数据就绪引脚开启(表示样本已经就绪,可以读取)之间的时间间隔。

图8.被采样的模拟输入和数据就绪切换之间的时间延迟。

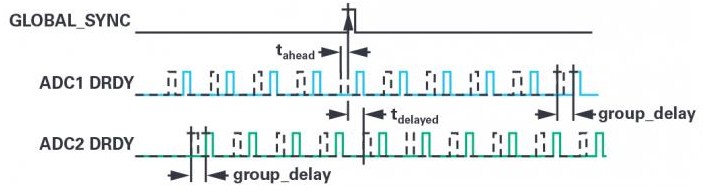

·如果采样时刻和Global_SYNC之间存在时间差,那么本地控制器会量化这个时间差(tahead或tdelayed),如图9所示。

图9.量化每个ADC的采样时刻(假设群延迟已知)和全局同步信号之间的时间差。

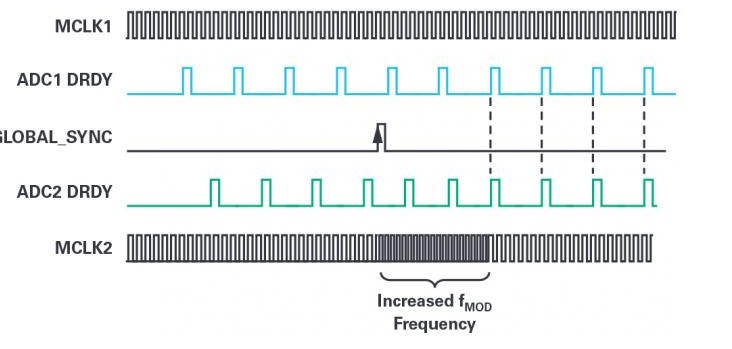

·如果存在差异,可以重新设置∑-∆滤波器,或者修改fMOD,以便在几个采样期间调整∑-∆采样。无论哪种情况,都可能漏掉几个样本。注意,通过改变局部时钟频率(fMOD),Σ-ΔADC会改变其输出数据速率(ODR=fMOD/N),如此,ADC会减慢或加快对模拟输入采样的速度,以期和系统中余下的ADC和Global_SYNC同步。

·如果fMOD被更新,那么在同步之后,主时钟频率会恢复到原来的频率,以返回到之前的ODR,而子系统则从该时刻开始同步。

在一段时间内改变fMOD的过程如图10所示。

图10.同步方法,采用PLL来调谐调制器的频率。

这种方法在某些情况下可能不适用,因为有几个细节需要考虑:

·将调制器频率更改为非整数倍值可能是不实际的。

·如果可以对频率进行微调,那么改变的频率步长必须很小,否则数字滤波器可能会超出限制,导致同步的实施时间变长。

·如果所需的ODR改变足够大,可以通过改变抽取率(N),而不是改变调制器频率(fMOD)来解决,但是,这也意味着会丢失一些样本。

·使用PLL意味着在达到期望的调制器频率之前,除了自身的建立时间之外,还会额外消耗功率。

一般来说,整个系统的复杂性和成本会随着系统规模的增大而增加,特别是与SAR ADC相比,对于后者,只需要将转换开始调整到与Global_SYNC信号匹配,即可轻松解决这个问题。此外,在许多情况下,因为存在上述系统限制,所以Σ-ΔADC无法使用。