3、工作原理

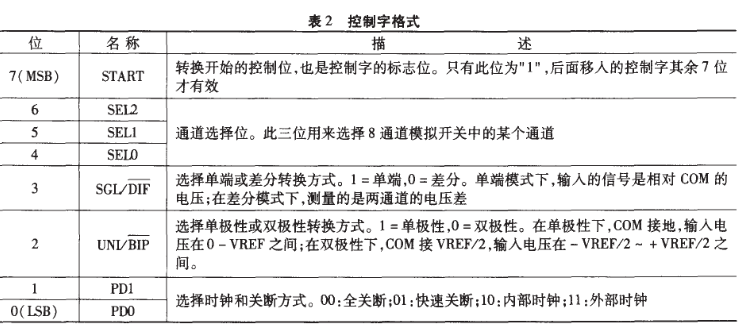

3.1控制字格式

在启动MAXll48进行A/D转换之前.必须先由SCLK将控制字从DIN端送入其内部输入移位寄存器,以决定其工作模式并启动转换。

3.2时钟模式

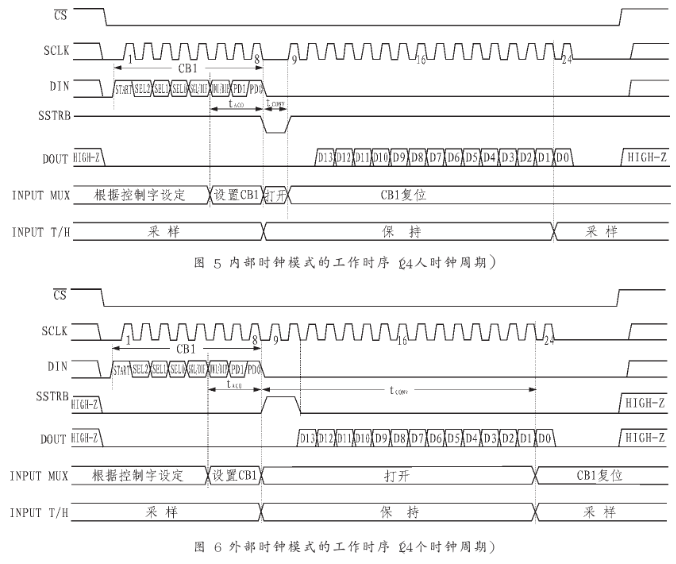

MAXll48可用外部串行时钟或内部时钟两种模式来完成逐次逼近转换。但是,不管哪种模式,数据的移人和移出都要由外部时钟SCLK来完成。

在外部时钟模式下,通过外部时钟SCLK控制数据的移入和移出,同时SCLK还是模数转换时钟。在控制字的最后一位移人后,SSTRB由低变高并在保持两个SCLK时钟周期的高电平后变低。其后14个SCLK的每一个下降沿决定逐次逼近转换结果每位的值,并在DOUT端输出。需要注意的是,每次模数转换都必须在较短时间内完成,以避免采样保持电容器上的压降对转换结果带来的影响。如果外部串行时钟SCLK的频率低于100kHz。或者由于串行时钟的不连续使得转换时间超过140μs,建议使用内部时钟模式。

在内部时钟模式时,MAXll48自身产生转换时钟,并允许微处理器以小于2.1MHz的时钟频率读取转换结果。在控制字的最后一位移入后,SSTRB由高变低,待转换完成后由低变高,完成一次转换的时间最长为8.0μs。在整个转换期间,为了得到最佳的噪声性能,SCLK应保持低电平。在SSTRB变为高电平之后,从第二个SCLK开始的每一个SCLK下降沿,在DOUT端由高到低依次输出转换结果的各位的值。

3.3 A/D转换过程

MAXll48在时钟脉冲的作用下进行逐次逼近式A/D转换,一般每24个时钟周期完成一次转换和读出操作。内部时钟模式与外部时钟模式的时序如图5、图6所示。

A/D转换速度要求不是很高时,常选用内部时钟模式。现以内部时钟模式为例说明MAXll48的工作过程:

首先根据系统要求确定MAXll48的控制字,例如,需转换0通道的单端单极性模拟量,控制字为8EH。然后向MAXll48输入控制字并读取转换结果,其步骤为:

(1)使片选端CS变为低电平并保持不变,此时DOUT处于低电平,SSTRB处于高电平;

(2)在DIN输入端由高到低依次输入控制字各位的值。

具体做法是:首先使DIN端为高电平(输入“l”),在第一个SCLK的上升沿将DIN的第一位数据“l”移入内部移位寄存器中。即移入START开始位:以此类推,在后面7个SCIJK的上升沿分别将输入DIN端的控制字其他位移入内部移位寄存器中;

(3)当控制字的最后一位数据被移入之后(第8个SCLK的下降沿),转换开始,SSTRB由高变低;